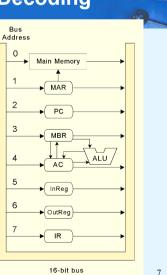

#### **4.8 MARIE**

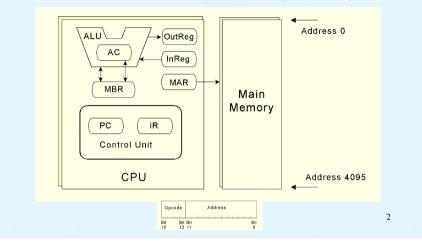

#### This is the MARIE architecture shown graphically.

#### 4.13 A Discussion on Decoding

- A computer's control unit keeps things synchronized, making sure that bits flow to the correct components as the bits are needed.

- There are two general ways in which a control unit can be implemented: *microprogrammed control* and *hardwired control*.

- With microprogrammed control, a small program is placed into read-only memory.

- Hardwired controllers implement this program using digital logic components.

5

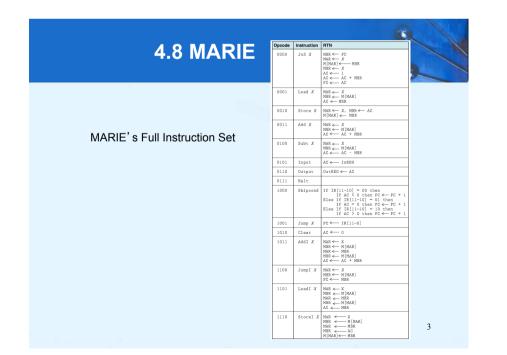

- Your text provides a complete list of the register transfer language for each of MARIE's instructions.

- The microoperations given by each RTL define the operation of MARIE's control unit.

- Each microoperation consists of a distinctive signal pattern that is interpreted by the control unit and results in the execution of an instruction.

- Recall, the RTL for the  $\ensuremath{\text{Add}}$  instruction is:

$\begin{array}{l} \text{mar} \leftarrow \mathbf{x} \\ \text{mbr} \leftarrow \mathbf{m}[\text{mar}] \\ \text{ac} \leftarrow \text{ac} + \text{mbr} \end{array}$

#### 4.13 A Discussion on Decoding

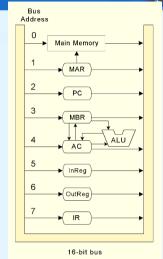

This is the MARIE data path shown graphically

Data and instructions are transferred using a common bus.

Some additional pathways speed up computation.

Data can be put on the common bus in the same clock cycle in which data can be put on these other pathways (allowing these events to take place in parallel).

6

8

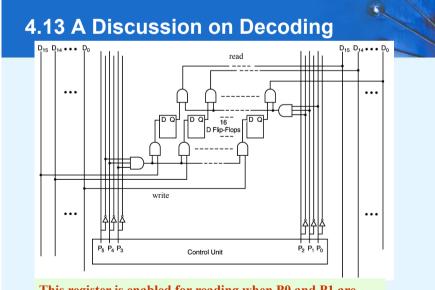

4.13 A Discussion on Decoding

- Let us define two sets of three signals.

- One set, P<sub>2</sub>, P<sub>1</sub>, P<sub>0</sub>, controls reading from memory or a register, and the other set consisting of P<sub>5</sub>, P<sub>4</sub>, P<sub>3</sub>, controls writing to memory or a register.

The next slide shows a close up view of MARIE's MBR.

This register is enabled for reading when P0 and P1 are high, and it is enabled for writing when P3 and P4 are high

- 0

- Careful inspection of MARIE's RTL reveals that the ALU has only three operations: add, subtract, and clear.

- We will also define a fourth "do nothing" state.

9

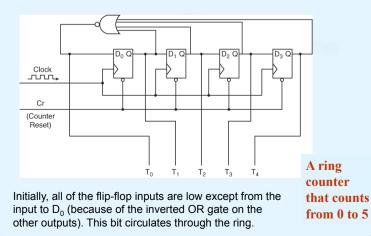

- The entire set of MARIE's control signals consists of:

- Register controls: P<sub>0</sub> through P<sub>5</sub>.

- ALU controls:  $A_0$  and  $A_1$

- Timing: T<sub>0</sub> through T<sub>7</sub> and counter reset  $C_r$

The counter is reset if fewer than eight clock cycles are needed for an instruction

# 4.13 A Discussion on Decoding

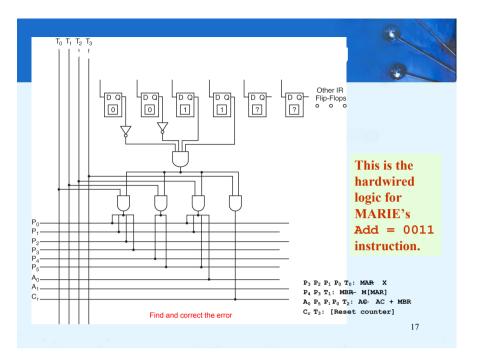

- Consider MARIE's Add instruction. It's RTL is:

MAR ← X

MBR ← M[MAR]

AC ← AC + MBR

- After an Add instruction is fetched, the address, X, is in the rightmost 12 bits of the IR, which has a datapath address of 7 (=111<sub>2</sub>).

- X is copied to the MAR, which has a datapath address of 1 (=001<sub>2</sub>).

- Thus we need to raise signals P<sub>2</sub>, P<sub>1</sub>, and P<sub>0</sub> to read from the IR, and signal P<sub>3</sub> to write to the MAR.

10

#### 4.13 A Discussion on Decoding 4.13 A Discussion on Decoding $C_3$ Τo · Here is the complete signal sequence for MARIE's · Notice the concurrent signal T<sub>1</sub> **Add** instruction: states during each machine Τ2 $P_3 P_2 P_1 P_0 T_0$ : MAR $\leftarrow X$ cycle: C<sub>0</sub> through C<sub>3</sub>. Тз $P_4 P_3 T_1: MBR \leftarrow M[MAR]$ P<sub>0</sub> $A_0 P_5 P_1 P_0 T_2$ : $AC \leftarrow AC + MBR$ P<sub>1</sub> C<sub>r</sub> T<sub>3</sub>: [Reset counter] $P_3 P_2 P_1 P_0 T_0$ : MAR $\leftarrow X$ $P_2$ These signals are ANDed with combinational logic to $P_4 P_3 T_1$ : MBR $\leftarrow$ M[MAR] $P_3$ bring about the desired machine behavior. $A_0 P_5 P_1 P_0 T_2$ : AC $\leftarrow$ AC + MBR $P_4$ • The next slide shows the timing diagram for this C<sub>r</sub> T<sub>3</sub>: [Reset counter] $P_5$ instruction. IR: 111, MAR: 001, Memory: 000, A<sub>0</sub> MBR: 011, AC: 100 C. 11 12 Timing diagram

13

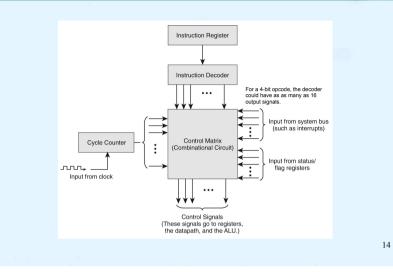

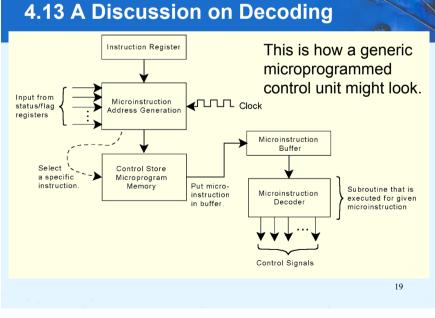

- We note that the signal pattern just described is the same whether our machine used hardwired or microprogrammed control.

- In *hardwired control*, the bit pattern of machine instruction in the IR is decoded by combinational logic.

- The decoder output works with the control signals of the current system state to produce a new set of control signals.

A block diagram of a hardwired control unit is shown on the following slide.

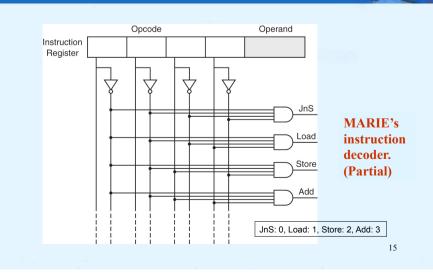

#### 4.13 A Discussion on Decoding

#### 4.13 A Discussion on Decoding

# 4.13 A Discussion on Decoding

4

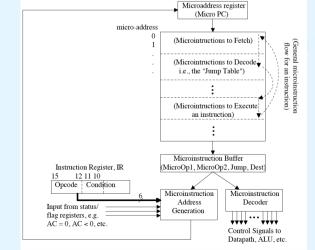

- In microprogrammed control, microcode instructions produces control signal changes.

- Machine instructions are the input for a microprogram that converts the 1s and 0s of an instruction into control signals.

- The microprogram is stored in firmware (ROM, PROM, or EPROM), which is also called the control store.

- A microcode instruction is retrieved during each clock cycle.

ROM: Read-Only Memory PROM: Programmable ROM EPROM: Erasable PROM

# a generic mmed might look.

ng

F

20

18

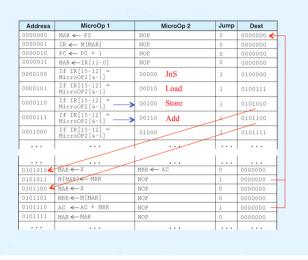

• If MARIE were microprogrammed, the microinstruction format might look like this:

| MicroOp1 | MicroOp2 | Jump | Dest |   |

|----------|----------|------|------|---|

| 17 13    | 12 8     | 7    | б    | 0 |

• MicroOp1 and MicroOp2 contain binary codes for each instruction. Jump is a single bit indicating that the value in the Dest field is a valid address and should be placed in the microsequencer (circuitry that that serves as the program counter).

Because some micro-instructions can be done in parallel (on the same tick of the clock), we will allow for two micro-operations to be carried out on each tick of the clock. 21

#### 4.13 A Discussion on Decoding

• The table below contains MARIE's microoperation codes along with the corresponding RTL:

| MicroOp<br>Code | Microoperation           | MicroOp<br>Code | Microoperation         |

|-----------------|--------------------------|-----------------|------------------------|

| 00000           | NOP                      | 01101           | MBR ← M[MAR]           |

| 00001           | $AC \leftarrow 0$        | 01110           | $OutREG \leftarrow AC$ |

| 00010           | AC $\leftarrow$ MBR      | 01111           | PC ← IR[11-0]          |

| 00011           | AC $\leftarrow$ AC - MBR | 10000           | PC ← MBR               |

| 00100           | AC $\leftarrow$ AC + MBR | 10001           | $PC \leftarrow PC + 1$ |

| 00101           | AC ← InREG               | 10010           | If $AC = 0$            |

| 00110           | IR ← M[MAR]              | 10011           | If AC > 0              |

| 00111           | M[MAR] ← MBR             | 10100           | If AC < 0              |

| 01000           | MAR ← IR[11-0]           | 10101           | If IR[11-10] = 00      |

| 01001           | MAR ← MBR                | 10110           | If IR[11-10] = 01      |

| 01010           | MAR ← PC                 | 10111           | If IR[11-10] = 10      |

| 01011           | MAR $\leftarrow$ X       | 11000           | If IR[15-12] =         |

| 01100           | MBR $\leftarrow$ AC      |                 | MicroOp2[4-1]          |

22

#### 4.13 A Discussion on Decoding

• The first nine lines of MARIE's microprogram are given below (using RTL for clarity):

| Address | MicroOp 1                       | MicroOp 2 | Jump | Dest    |

|---------|---------------------------------|-----------|------|---------|

| 0000000 | $MAR \leftarrow PC$             | NOP       | 0    | 0000000 |

| 0000001 | $IR \leftarrow M[MAR]$          | NOP       | 0    | 0000000 |

| 0000010 | $PC \leftarrow PC + 1$          | NOP       | 0    | 0000000 |

| 0000011 | MAR $\leftarrow$ IR[11-0]       | NOP       | 0    | 0000000 |

| 0000100 | If IR[15-12] =<br>Micro0p2[4-1] | 00000     | 1    | 0100000 |

| 0000101 | If IR[15-12] =<br>Micro0p2[4-1] | 00010     | 1    | 0100111 |

| 0000110 | If IR[15-12] =<br>Micro0p2[4-1] | 00100     | 1    | 0101010 |

| 0000111 | If IR[15-12] =<br>Micro0p2[4-1] | 00110     | 1    | 0101100 |

| 0001000 | If IR[15-12] =<br>Micro0p2[4-1] | 01000     | 1    | 0101111 |

|         |                                 |           |      |         |

#### 4.13 A Discussion on Decoding

- The first four lines initiates the fetch-decode-execute cycle.

- The remaining lines are the beginning of a jump table.

| Address | MicroOp 1                       | MicroOp 2 | Jump | Dest    |

|---------|---------------------------------|-----------|------|---------|

| 0000000 | $MAR \leftarrow PC$             | NOP       | 0    | 0000000 |

| 0000001 | $IR \leftarrow M[MAR]$          | NOP       | 0    | 0000000 |

| 0000010 | $PC \leftarrow PC + 1$          | NOP       | 0    | 0000000 |

| 0000011 | MAR $\leftarrow$ IR[11-0]       | NOP       | 0    | 0000000 |

| 0000100 | If IR[15-12] =<br>Micro0p2[4-1] | 00000     | 1    | 0100000 |

| 0000101 | If IR[15-12] =<br>Micro0p2[4-1] | 00010     | 1    | 0100111 |

| 0000110 | If IR[15-12] =<br>Micro0p2[4-1] | 00100     | 1    | 0101010 |

| 0000111 | If IR[15-12] =<br>Micro0p2[4-1] | 00110     | 1    | 0101100 |

| 0001000 | If IR[15-12] =<br>Micro0p2[4-1] | 01000     | 1    | 0101111 |

|         |                                 |           |      |         |

25

#### 4.13 A Discussion on Decoding

4.13 A Discussion on Decoding

- It's important to remember that a microprogrammed control unit works like a system in miniature.

- Microinstructions are fetched, decoded, and executed in the same manner as regular instructions.

- This extra level of instruction interpretation is what makes microprogrammed control slower than hardwired control.

- The advantages of microprogrammed control are that it can support very complicated instructions and only the microprogram needs to be changed if the instruction set changes (or an error is found). Microprogrammed control dominates the personal computer market.

#### 4.13 A Discussion on Decoding

The microinstructions for the Store and Add instructions.

| Address | MicroOp 1                | MicroOp 2           | Jump | Dest    |  |

|---------|--------------------------|---------------------|------|---------|--|

|         |                          |                     |      |         |  |

|         |                          |                     |      |         |  |

|         |                          |                     |      |         |  |

| 0101010 | MAR $\leftarrow$ X       | $MBR \leftarrow AC$ | 0    | 000000  |  |

| 0101011 | $M[MAR] \leftarrow MBR$  | NOP                 | 1    | 0000000 |  |

| 0101100 | $MAR \leftarrow X$       | NOP                 | 0    | 0000000 |  |

| 0101101 | $MBR \leftarrow M[MAR]$  | NOP                 | 0    | 0000000 |  |

| 0101110 | $AC \leftarrow AC + MBR$ | NOP                 | 1    | 0000000 |  |

|         |                          |                     |      |         |  |

|         |                          |                     |      |         |  |

|         |                          |                     |      | 26      |  |

|         |                          |                     |      |         |  |

#### 4.14 Real World Architectures

- MARIE shares many features with modern architectures but it is not an accurate depiction of them.

- In the following slides, we briefly examine two machine architectures.

- We will look at an Intel architecture, which is a CISC machine and MIPS, which is a RISC machine.

- CISC is an acronym for complex instruction set computer.

- RISC stands for reduced instruction set computer.

We delve into the "RISC versus CISC" argument in Chapter 9.

#### 4.14 Real World Architectures

- The classic Intel architecture, the 8086, first member of the x86 family, was born in 1979. It is a CISC architecture.

- It was adopted by IBM for its famed PC (later dubbed the XT), which was released in 1981.

- The 8086 operated on 16-bit data words and supported 20-bit memory addresses.

- Later, to lower costs, the 8-bit bus 8088 was introduced. Like the 8086, it used 20-bit memory

What was the largest memory that the 8086 could address?

29

#### 4.14 Real World Architectures

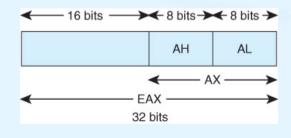

- In 1985, Intel introduced the 32-bit 80386.

An "E" prefix (which stood for "extended") was added to the register names (EAX, EBX, ECX, and EDX).

- It also had no built-in floating-point unit.

- The 80486, introduced in 1989, was an 80386 that had built-in floating-point processing and cache memory.

- The 80386 and 80486 offered downward compatibility with the 8086 and 8088.

- Software written for the smaller word systems was directed to use the lower 16 bits of the 32-bit registers.

#### 4.14 Real World Architectures

- The 8086 had four 16-bit general-purpose registers (AX, BX, CX, and DX) that could be accessed by the half-word.

- It also had a flags register, an instruction register, and a stack accessed through the values in two other registers, the stack pointer (SP) and the base pointer (BP). SP was used to reference the top of the stack. BP was used to reference parameters pushed onto the stack.

- The 8086 had no built in floating-point processing.

- In 1980, Intel released the 8087 numeric coprocessor, but few users elected to install them because of their cost.

### 4.14 Real World Architectures

EAX register, broken into parts

#### 4.14 Real World Architectures

- Intel's Pentium 4 (2000) introduced a brand new NetBurst architecture.

- Speed enhancing features include:

- Hyperthreading

- Hyperpipelining

- Wider instruction pipeline

- Execution trace cache (holds decoded instructions for possible reuse) multilevel cache and instruction pipelining.

- Intel, along with many others, is marrying many of the ideas of RISC architectures with microprocessors that are largely CISC.

33

#### 4.14 Real World Architectures

- MIPS was one of the first RISC microprocessors.

- The original MIPS architecture had only 55 different instructions, as compared with the 8086 which had over 100.

- MIPS was designed with performance in mind: It is a *load/store* architecture, meaning that only the load and store instructions can access memory.

- The large number of registers in the MIPS architecture keeps bus traffic to a minimum.

#### How does this design affect performance?

#### 4.14 Real World Architectures

- The MIPS family of CPUs has been one of the most successful in its class.

- In 1986 the first MIPS CPU was announced.

- It had a 32-bit word size and could address 4GB of memory.

- Over the years, MIPS processors have been used in general purpose computers as well as in games (Nintendo and Sony).

- The MIPS architecture now offers 32- and 64-bit versions.

34

#### **Chapter 4 Conclusion**

- The major components of a computer system are its control unit, registers, memory, ALU, and data path.

- A built-in clock keeps everything synchronized.

- Control units can be microprogrammed or hardwired.

- Hardwired control units give better performance, while microprogrammed units are more adaptable to changes.

### **Chapter 4 Conclusion**

- Computers run programs through iterative fetchdecode-execute cycles.

- Computers can run programs that are in machine language.

- An assembler converts mnemonic code to machine language.

- The Intel architecture is an example of a CISC architecture; MIPS is an example of a RISC architecture.

37

#### **End of Chapter 4**

38